DIFERENCIAS ENTRE LOS MODELOS DE VON NEUMANN Y HARVARD

Antes de comparar el modelo de Von Neumann con el de Harvard debemos poder diferenciar estos por separado.

MODELO DE ARQUITECTURA DE VON NEUMANN

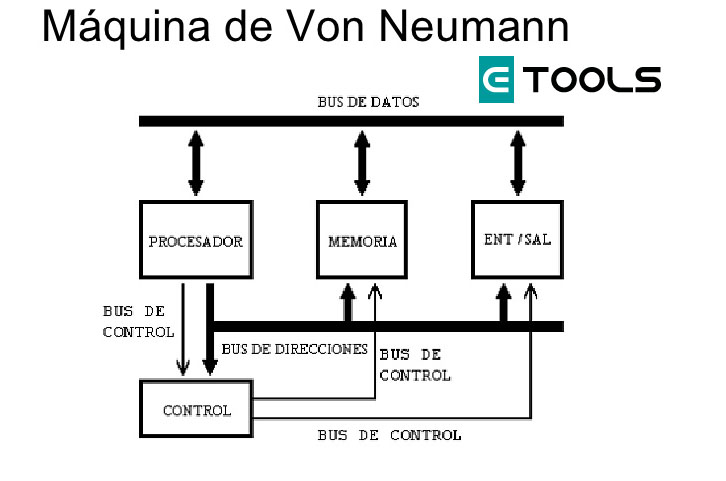

La arquitectura de John Von Neumann se caracteriza principalmente por los procesadores que tiene el mismo dispositivo de almacenamiento tanto para las instrucciones como para los datos. Estos, al ser almacenados en el mismo formato dentro de la memoria, utiliza un único bus de datos para poder mantener contacto con la CPU. Esto crea una eficiencia en la utilización de la memoria, pero al mismo tiempo requiere una ambigüedad para poder reconocer y distinguir los datos. Los ordenadores que utilizan este modelo se componen por la unidad aritmética lógica o “ALU”

La arquitectura de John Von Neumann se caracteriza por los procesadores que poseen el mismo dispositivo de almacenamiento tanto para los datos como para las instrucciones.

Al ser almacenados en el mismo formato dentro de la misma memoria, utilizan un único bus de datos para comunicarse con la CPU. Esto hace que este tipo sea eficiente en la utilización de memoria, pero que requiera una ambigüedad para reconocer los datos.

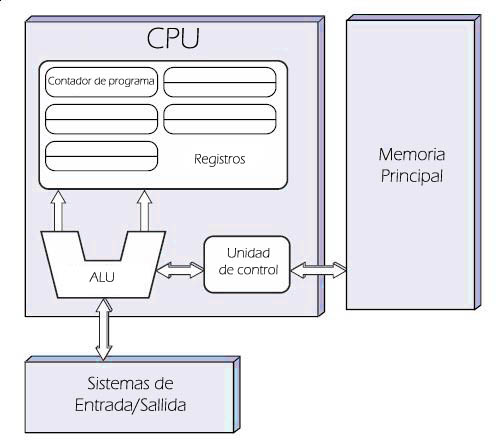

Los ordenadores de este tipo se componen de la unidad aritmético-lógica o "ALU", la unidad de control, una memoria, un dispositivo de entrada y salida y un bus de datos que los comunica.

Esta arquitectura es una familia de arquitecturas de computadoras que utilizan el mismo dispositivo para almacenar como para las instrucciones.

Los ordenadores con la arquitectura de Von Neumann constan de cinco partes: La Unidad Aritmética Lógica (ALU), la unidad de control, la memoria, un dispositivo de entrada/salida y el bus de datos que proporciona un medio para transportar los datos entre las distintas partes.

Un ordenador que posea esta arquitectura emula los siguientes procedimientos:

- Al encender el ordenador y obtener la siguiente instrucción desde la memoria en la dirección indicada por el contador de programa y la guarda en el registro de instrucciones.

- Aumenta el contador de programa y lo guarda en el registro de instrucción.

- Decodifica la instrucción a través de la unidad de control. Ésta es la encargada de coordinar el resto de los componentes de la computadora para realiza cada función determinada.

- Se ejecuta la instrucción. Ésta puede cambiar el valor del contador de programa, permitiendo hacer operaciones repetitivas. El contador puede cambiar también cuando se cumpla una cierta condición aritmética, haciendo que el ordenador pueda “pensar”, haciendo que pueda alcanzar cualquier grado de complejidad a través de la aritmética y de la lógica anteriores.

Hoy en día, la mayoría de las computadoras son construidas con esta arquitectura ya que las capacidades dnámicas del diseño, como la implementacion y la operación de un programa en vez de dos, aunque puede ser más lenta para determinadas tareas, es mas flexible y permite mas conceptos como la programación libre.

MODELO DE ARQUITECTURA DE HARVARD

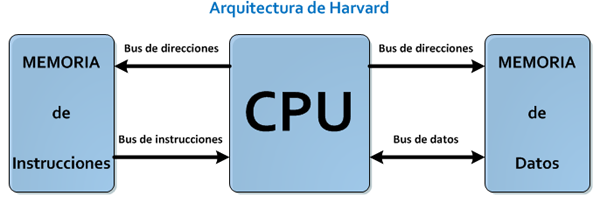

A diferencia del modelo de Von Neumann, el modelo de arquitectura de Harvard, que proviene del Harvard Mark I, se diferencia principalmente por la división de las instrucciones de los datos que se comunican con la unidad central de proceso en dos memorias separadas. Esto genera también que se utilicen distintos buses de información. Aunque es común un único bus de direcciones, con un control que pueda diferenciar entre ambas memorias. Al contrario del modelo de arquitectura de John Von Neumann, el modelo de Harvard no requiere de la ambigüedad para poder reconocer los datos, pero no es tan eficiente en la utilización de la memoria. Estos ordenadores siempre se componen por los mismos elementos que los utilizados por el modelo de Von Neumann, excepto por que tiene dos memorias, una utilizada para las instrucciones y otra para los datos, y no una única memoria como el otro modelo.

En este modelo, las instrucciones y los datos se almacenan en cachés diferentes para mejorar el rendimiento. Pero por su contraparte, tiene el inconveniente de tener que dividir la cantidad de memoria caché entre los dos, por lo que funciona mejor sólo en los casos particulares cuando la frecuencia de lectura de instrucciones y de datos es aproximadamente la misma.

Resumidamente, la arquitectura de Harvard se basa en:

- Las instrucciones y los datos se almacenan en caches separadas para mejorar el rendimiento.

- Tienen el inconveniente de tener que dividir las memorias caches entre los dos, por lo que no funciona de la mejor manera, salvo cuando la frecuencia de lectura de instrucciones y de datos es aproximadamente la misma.

- Esta arquitectura suele utilizarse en DSPs, o procesador de seal digital, usados prácticamente siempre en los productos para el procesamiento de audio y vídeo.

En el siguiente artículo hablaremos sobre la arquitectura de Pipeline, no dudes pasar para leer la nota y seguir informándote acerca de las arquitecturas de la computadora.

¡Si te gustó el artículo no dudes en dejar un comentario!

Si quieres conocer otros artículos parecidos a DIFERENCIAS ENTRE LOS MODELOS DE VON NEUMANN Y HARVARD puedes visitar la categoría Electrónica digital.

-

Gracias!

-

El tema es muy claro y fácil de entender, muchas gracias

-

Información clara y util. Gracias al autor.

-

Me ha valido mucho esta información. Muchas gracias!!!!!

Deja un comentario

Gracias por el posteo. Me resultó bastante útil